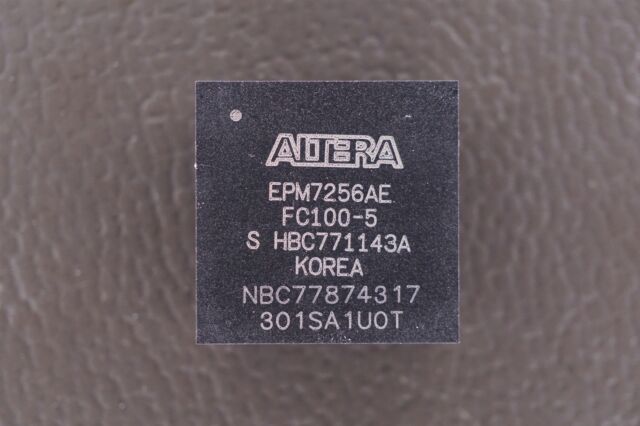

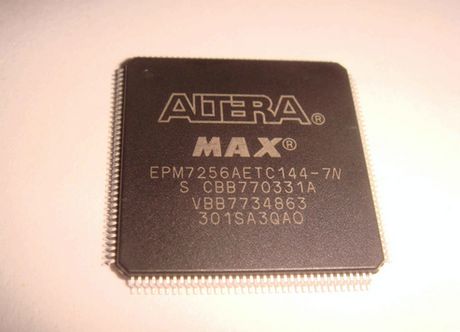

Altera PLD EPM7256AEFC100-7 Eeprom File Dumping

Altera PLD EPM7256AEFC100-7 Eeprom File Dumping needs to attack pld epm7256bti144 security fuse bit, and then extract eeprom data from altera pld epm7256aefc100;

SENDB is automatically cleared by hardware when the Break signal has been sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character to unlock altera cpld epm7128aetc100 memory program (typically, the Sync character in the LIN specification).

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission.

To send a Break Signal:

- Configure the EUSART for asynchronous trans- missions (steps 1-5). Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (see Section 16.2 “EUSART Baud Rate Generator (BRG)”).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

If interrupts are desired, set enable bit TXIE

- If 9-bit transmission is desired, set transmit bit TX9. Can be used as address/data bit to crack intel cpld epm7128btc100.

- Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- Set the SENDB bit.

- Load a byte into TXREG. This triggers sending a Break signal. The Break signal is complete when TRMT is set. SENDB will also be cleared.

See Figure 16-9 for the timing of the Break signal sequence.

Tags: Altera PLD EPM7256AEFC100-7 Eeprom File Dumping deve attaccare pld epm7256bti144 security fuse bit ed estrarre i dati eeprom da altera pld epm7256aefc100,Altera PLD EPM7256AEFC100-7 Eeprom File Dumping potřebuje zaútočit na bezpečnostní pojistkový bit pld epm7256bti144 a extrahovat data eeprom z altera pld epm7256aefc100,Altera PLD EPM7256AEFC100-7 Le vidage de fichiers Eeprom doit attaquer le bit de fusible de sécurité pld epm7256bti144 et extraire les données eeprom d'altera pld epm7256aefc100