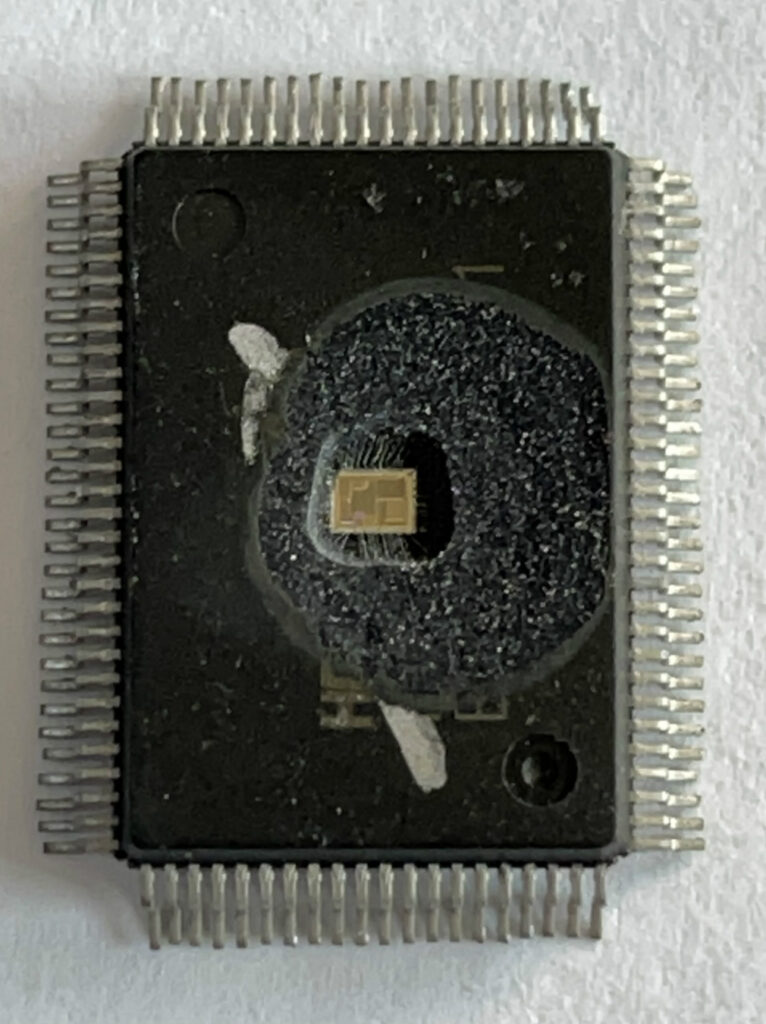

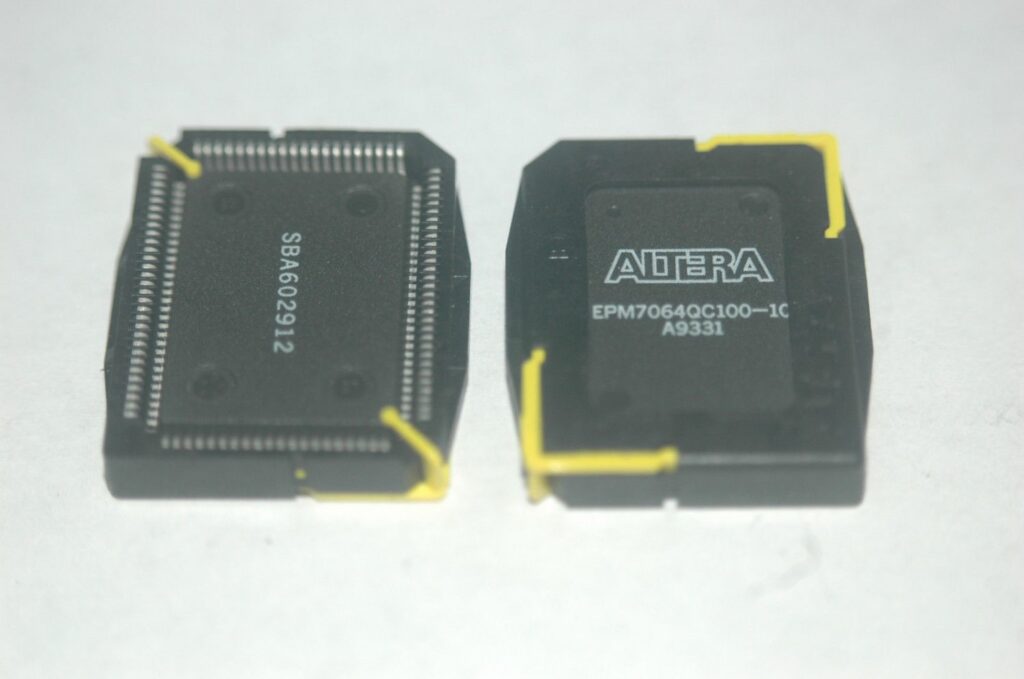

Altera CPLD EPM7064QC100-12 Eeprom POF Program Replication

Altera CPLD EPM7064QC100-12 Eeprom POF Program Replication will help engineer to recover cpld chip epm7064ac100 embedded software from its eeprom memory, the security fuse bit of cpld IC EPM7064QC100 will be unlocked;

See the Operating Requirements for Altera Devices Data Sheet.

Minimum DC input voltage is –0.5 V. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns. For EPM7128A and EPM7256A devices only, VCC must rise monotonically by cloning cpld epm7064slc44 eeprom pof file. In MAX 7000AE devices, all pins, including dedicated inputs, I/O pins, and JTAG pins, may be driven before VCCINT and VCCIO are powered.

These devices support in-system programming for –40° to 100° C. For in-system programming support between –40° and 0° C, contact Altera Applications.

These values are specified under the recommended operating conditions shown in Table 14 on page 28. The parameter is measured with 50% of the outputs each sourcing the specified current. The IOH parameter refers to high-level TTL or CMOS output current.

The parameter is measured with 50% of the outputs each sinking the specified current. The IOL parameter refers to low-level TTL or CMOS output current.

This value is specified for normal device operation. For MAX 7000AE devices, the maximum leakage current during power-up is ±300 mA when copy altera cpld epm7064sti44 binary program. For EPM7128A and EPM7256A devices, leakage current during power-up is not specified. For EPM7128A and EPM7256A devices, this pull-up exists while a device is programmed in-system.