Altera CPLD EPM7064LI84-10 Chip Eeprom Program Duplication

Altera CPLD EPM7064LI84-10 Chip Eeprom Program Duplication will need to break epm7064lc68 cpld chip protection, the original cpld epm7064li84 chip will be decapsulated with focus ion beam technique;

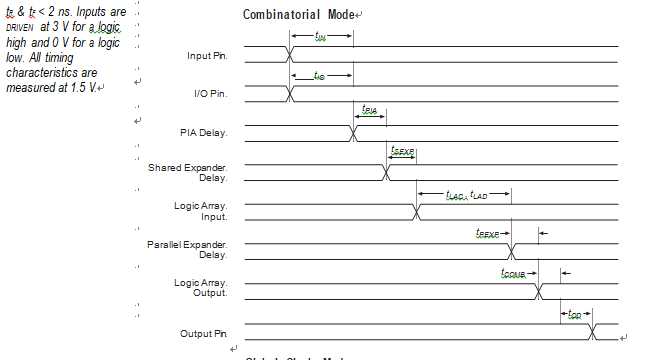

MAX 7000A device timing can be analyzed with the Altera software, a variety of popular industry-standard EDA simulators and timing analyzers, or with the timing model shown in below Figure. MAX 7000A devices have predictable internal delays that enable the designer to determine the worst-case timing of any design which can be used for retriving altera cpld epm7064stc44 code.

The software provides timing simulation, point-to-point delay prediction, and detailed timing analysis for device-wide performance evaluation.

The timing characteristics of any signal path can be derived from the timing model and parameters of a particular device. External timing parameters, which represent pin-to-pin timing delays, can be calculated as the sum of internal parameters to break altera cpld epm7064lc68. Below Figure shows the timing relationship between internal and external delay parameters.