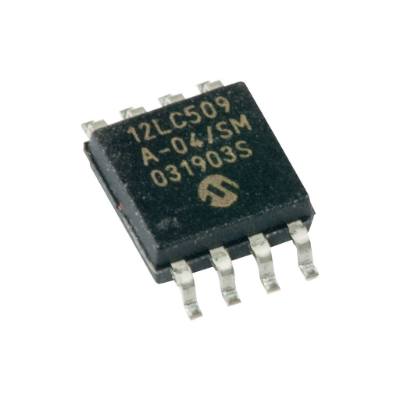

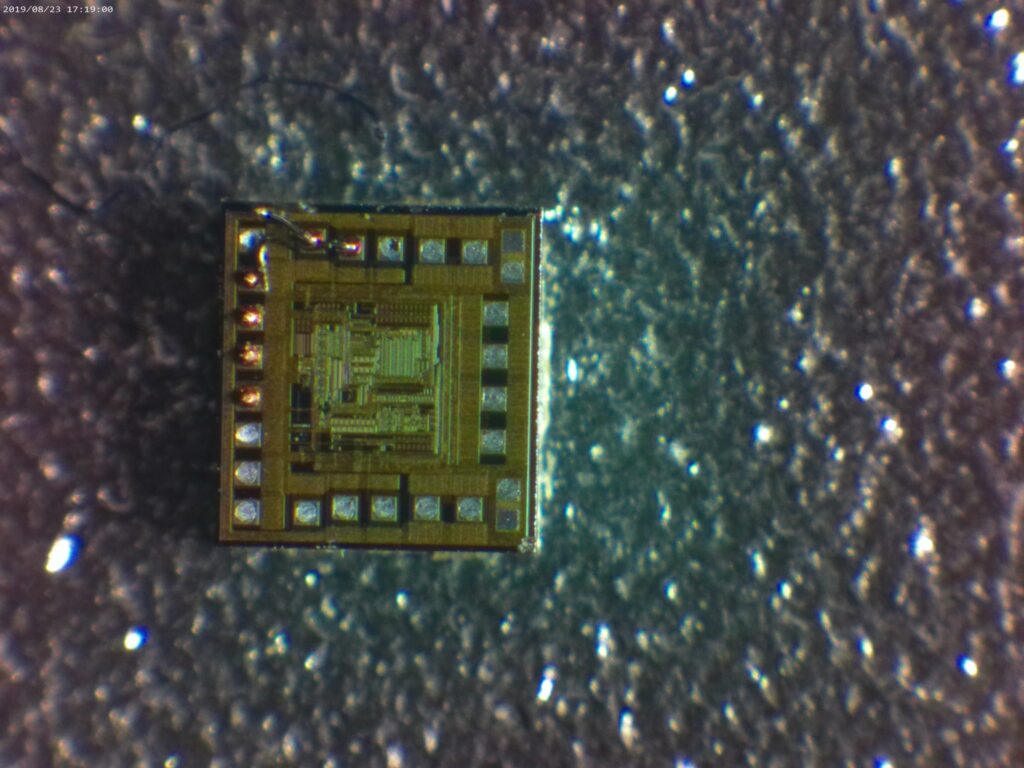

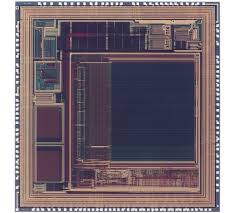

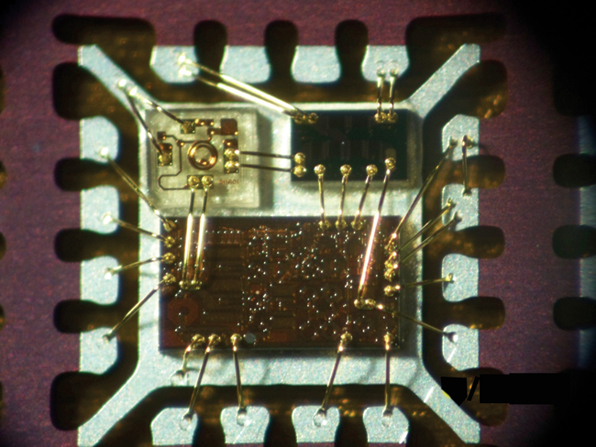

PIC12LC509A MCU Program Data Cracking

PIC12LC509A MCU program data cracking including attack encrypted PIC12LC509A microcontroller fuse bit and extract embedded firmware from PIC12LC509A Microchip microprocessor flash program memory and eeprom data memory, the source code being readout from original master PIC12LC509A microcomputer is in the format of binary file or heximal data;

PIC12LC509A devices have a 12-bit wide hardware push/pop stack. A CALL instruction will push the current value of stack 1 into stack 2 and then push the current program counter value when Crack TMS320F28031 DSP MCU Locked Memory, incremented by one, into stack level 1 to perform the PIC12LC509A MCU Program Data Cracking. If more than two sequential CALL’s are executed, only the most recent two return addresses are stored.

A RETLW instruction will pop the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1 after Reverse Engineering Microcontroller. If more than two sequential RETLW’s are executed, the stack will be filled with the address previously stored in level 2.

Note that the W register will be loaded with the literal value specified in the instruction from Unlock ARM MCU STM32F100C6 Memory. This is particularly useful for the implementation of data look-up tables within the program memory.

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer). This is indirect addressing.

EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 07 contains the value 10h

- Register file 08 contains the value 0Ah

- Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h from Unlock IC PIC16C74B Binary. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). A simple program to clear RAM locations 10h-1Fh using indirect addressing.

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF PORTB,W) always read the I/O pins independent of the pin’s input/output modes from Samsung S3F94C8 MCU Unlocking. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set.