Motorola MC68HC08AS32 Memory Program Cloning

The configuration registers are used in the initialization of various options and bring great benefit for Motorola MC68HC08AS32 Memory Program Cloning.

The configuration registers can be written once after each reset. All of the configuration register bits are cleared during reset. Since the various options affect the operation of the MCU, it is recommended that these registers be written immediately after reset.

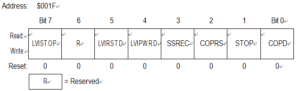

The configuration registers are located at $001F and $003F. The configuration register may be read at anytime.

LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate in stop mode. Reset clears LVISTOP and Freescale MC68HC11KS2 Memory Program Cloning.

- Low-Voltage Inhibit (LVI).)

1 = LVI enabled during stop mode 0 = LVI disabled during stop mode

LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module. (See Section 21. Low-Voltage Inhibit (LVI).) 1 = LVI module resets disabled

0 = LVI module resets enabled

LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module. (See Section 21. Low-Voltage Inhibit (LVI).)

1 = LVI module power disabled 0 = LVI module power enabled

SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 CGMXCLK cycles instead of a 4096 CGMXCLK cycle delay.

1 = STOP mode recovery after 32 CGMXCLK cycles

0 = STOP mode recovery after 4096 CGMXCLK cycles from RECOVER MCU