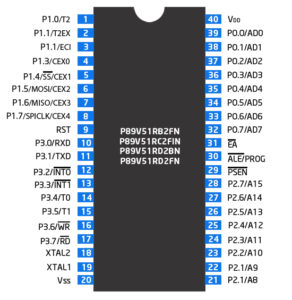

Philip MCU P89V51RB2 Program Memory Extraction

PHILIP MCU P89V51RB2 Program Memory Extraction refers to the content being extrated out from its flash and eeprom memory, below we will present the general description about this microcontroller:

The P89V51RB2 are 80C51 microcontrollers with 16/32/64 kB Flash and 1024 bytes of data RAM. A key feature of the P89V51RB2 is its X2 mode option.

The design engineer can choose to run the application with the conventional 80C51 clock rate (12 clocks per machine cycle) or select the X2 mode (6 clocks per machine cycle) to achieve twice the throughput at the same clock frequency in the process of Microcontroller copying.

Another way to benefit from this feature is to keep the same performance by reducing the clock frequency by half, thus dramatically reducing the EMI.

The Flash program memory supports both parallel programming and in serial In-System Programming (ISP). Parallel programming mode offers gang-programming at high speed, reducing programming costs and time to market.

ISP allows a device to be reprogrammed in the end product under software control. The capability to field/update the application firmware makes a wide range of applications possible. The P89V51RB2/RC2/RD2 is also In-Application Programmable (IAP), allowing the Flash program memory to be reconfigured even while the application is running.

80C51 Central Processing Unit

5 V Operating voltage from 0 MHz to 40 MHz

16/32/64 kB of on-chip Flash user code memory with ISP (In-System Programming) and IAP (In-Application Programming)

Supports 12-clock (default) or 6-clock mode selection via software or ISP SPI (Serial Peripheral Interface) and enhanced UART

PCA (Programmable Counter Array) with PWM and Capture/Compare functions Four 8-bit I/O ports with three high-current Port 1 pins (16 mA each)

Three 16-bit timers/counters Programmable watchdog timer

Eight interrupt sources with four priority levels Second DPTR register

Low EMI mode (ALE inhibit)

TTL- and CMOS-compatible logic levels