NXP P87C054 Microprocessor Memory Program Copying

In applications using the Hardware Watchdog Timer of the P87C054, a series resistor (1Kfi T20%) needs to be included between the reset pin and any external components. Without this resistor the watchdog timer will not function.

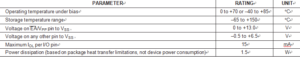

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated Parameters are valid over operating temperature range unless otherwise All voltages are with respect to VSS unless otherwise noted.

NOTES:

1. Typical ratings are not guaranteed. The values listed are at room temperature, 5V.

2. Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the VOLs of ALE and ports 1 and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V from NXP P87C054 Microprocessor Memory Program Copying.

In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. IOL can exceed these conditions provided that no single output sinks more than 5mA and no more than two outputs exceed the test conditions.

3. Capacitive loading on ports 0 and 2 may cause the VOH on ALE and PSEN to momentarily fall below the VCC–0.7 specification when the address bits are stabilizing.

4. Pins of ports 1, 2 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when VIN is approximately 2V.

5. See Figures 37 through 40 for ICC test conditions, and Figure 36 for ICC vs Freq.

Active mode: ICC = (0.9 FREQ. + 1.1)mA for all devices except 8XC51RD+; 8XC51RD+ ICC = (0.9 x Freq +2.1) mA Idle mode: ICC = (0.18 FREQ. +1.01)mA

6. This value applies to Tamb = 0C to +70C. For Tamb = –40C to +85C, ITL = –750A.

7. Load capacitance for port 0, ALE, and PSEN = 100pF, load capacitance for all other outputs = 80pF.

8. Under steady state (non-transient) conditions, IOL must be externally limited as follows: Maximum IOL per port pin: 15mA (*NOTE: This is 85C specification.) Maximum IOL per 8-bit port: 26mA

Maximum total IOL for all outputs: 71mA

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

9. ALE is tested to VOH1, except when ALE is off then VOH is the voltage specification.

10. Pin capacitance is characterized but not tested. Pin capacitance is less than 25pF. Pin capacitance of ceramic package is less than 15pF (except EA is 25pF).