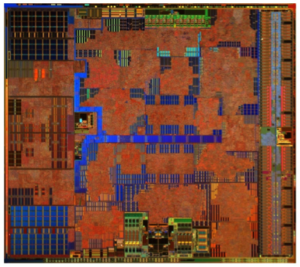

Hack CPLD IC Altera EPM240T100A MAX II Device

We can Hack CPLD IC Altera EPM240T100A MAX II Device, please view the IC chip features for your reference:

The MAX II CPLD has the following features:

Low-cost, low-power CPLD

Instant-on, non-volatile architecture

Standby current as low as 29 µA

Provides fast propagation delay and clock-to-output times

Provides four global clocks with two clocks available per logic array block (LAB)

UFM block up to 8 Kbits for non-volatile storage to Crack Microcontroller STM32F103R6

MultiVolt core enabling external supply voltages to the device of either 3.3 V/2.5 V or 1.8 V

MultiVolt I/O interface supporting 3.3-V, 2.5-V, 1.8-V, and 1.5-V logic levels

Bus-friendly architecture including programmable slew rate, drive strength, bus-hold, and programmable pull-up resistors from Break IC Program

Schmitt triggers enabling noise tolerant inputs (programmable per pin)

I/Os are fully compliant with the Peripheral Component Interconnect Special

Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 for 3.3-V operation at 66 MHz

Supports hot-socketing

Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990

ISP circuitry compliant with IEEE Std. 1532

MAX II devices are available in space-saving FineLine BGA, Micro FineLine BGA, and thin quad flat pack (TQFP) packages (refer to Table 1–3 and 1–3). MAX II devices support vertical migration within the same package (for example, you can migrate between the EPM570, EPM1270, and EPM2210 devices in the 256-pin FineLine BGA package) for the purpose of Recovery IC CPLD Chip Xilinx XC9536XL-10VQG44C.

Vertical migration means that you can migrate to devices whose dedicated pins and JTAG pins are the same and power pins are subsets or supersets for a given package across device densities.

The largest density in any package has the highest number of power pins; you must lay out for the largest planned density in a package to provide the necessary power pins for migration. For I/O pin migration across densities, cross reference the available I/O pins using the device pin-outs for all planned densities of a given package type to identify which I/O pins can be migrated for the purpose of Extract MCU IC NXP P89LPC925FDH. The Quartus® II software can automatically cross-reference and place all pins for you when given a device migration list.

Tags: hack cpld ic flash content,hack cpld ic heximal file,hack cpld ic protect eprom,hack cpld ic software memory,hack cpld ic source code