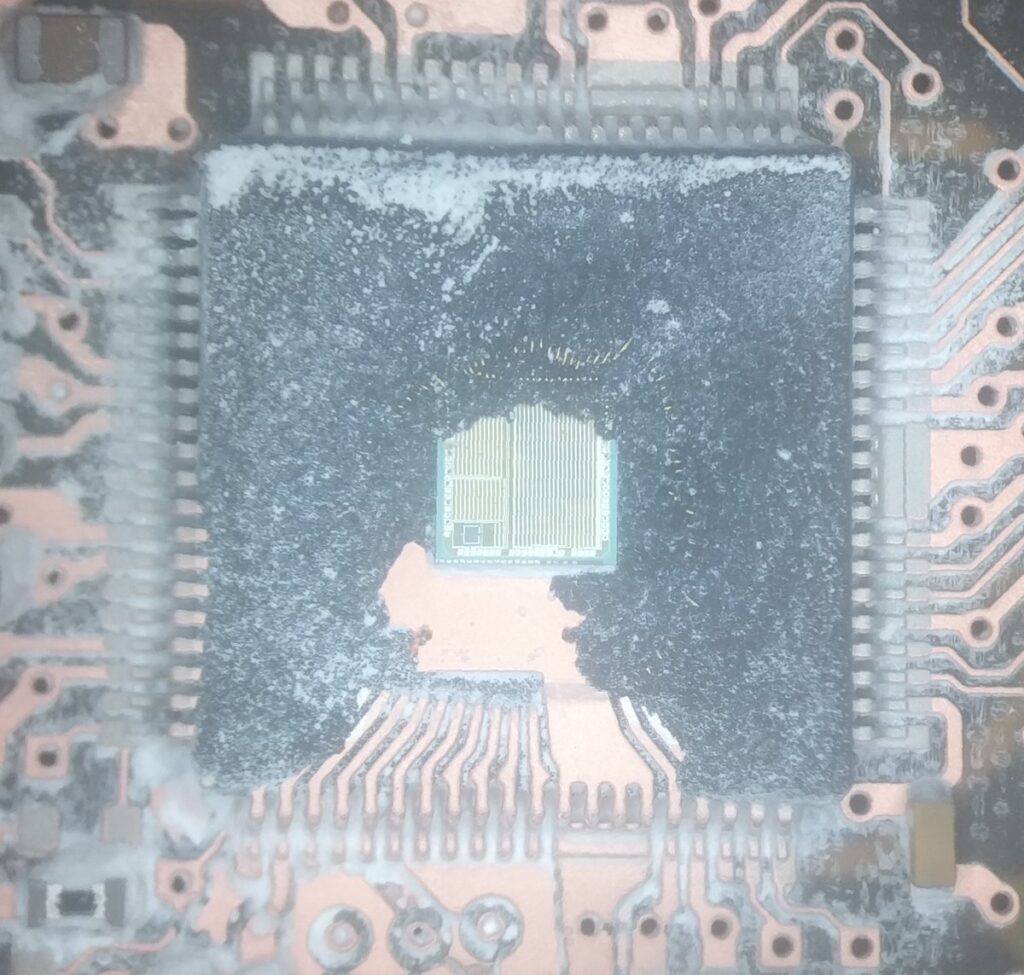

Copy ATMEGA48V Secured MCU Flash Code

Copy ATMEGA48V Secured MCU Flash Code including the program inside flash memory and data from eeprom memory, embedded firmware will be recovered from atmega48v microcontroller, locked status of processor atmega48v will be modified then programmer can read mcu heximal out from it directly;

When the SM2:0 bits are written to 000, the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing SPI, USART, Analog Comparator, ADC, Two-wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue operating. This sleep mode basically halts clkCPU and clkFLASH, while allowing the other clocks to run.

Idle mode enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and USART Transmit Complete interrupts.

If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Status Register – ACSR when clone atmega48 microprocessor flash binary. This will reduce power consumption in Idle mode. If the ADC is enabled, a conver- sion starts automatically when this mode is entered.

When the SM2:0 bits are written to 001, the SLEEP instruction makes the MCU enter ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the external interrupts to replicate atmega48p mcu flash code, the Two-wire Serial Interface address watch, Timer/Counter2 and the Watchdog to continue operating (if enabled). This sleep mode basically halts clkI/O, clkCPU, and clkFLASH, while allowing the other clocks to run.

Tags: reproduire ATMEGA48V binaire de mémoire flash de puce MCU verrouillée,reproduire ATMEGA48V code micrologiciel sécurisé du microprocesseur,reproduire ATMEGA48V fichier logiciel protégé du micro-ordinateur,reproduire ATMEGA48V programme heximal de microcontrôleur crypté