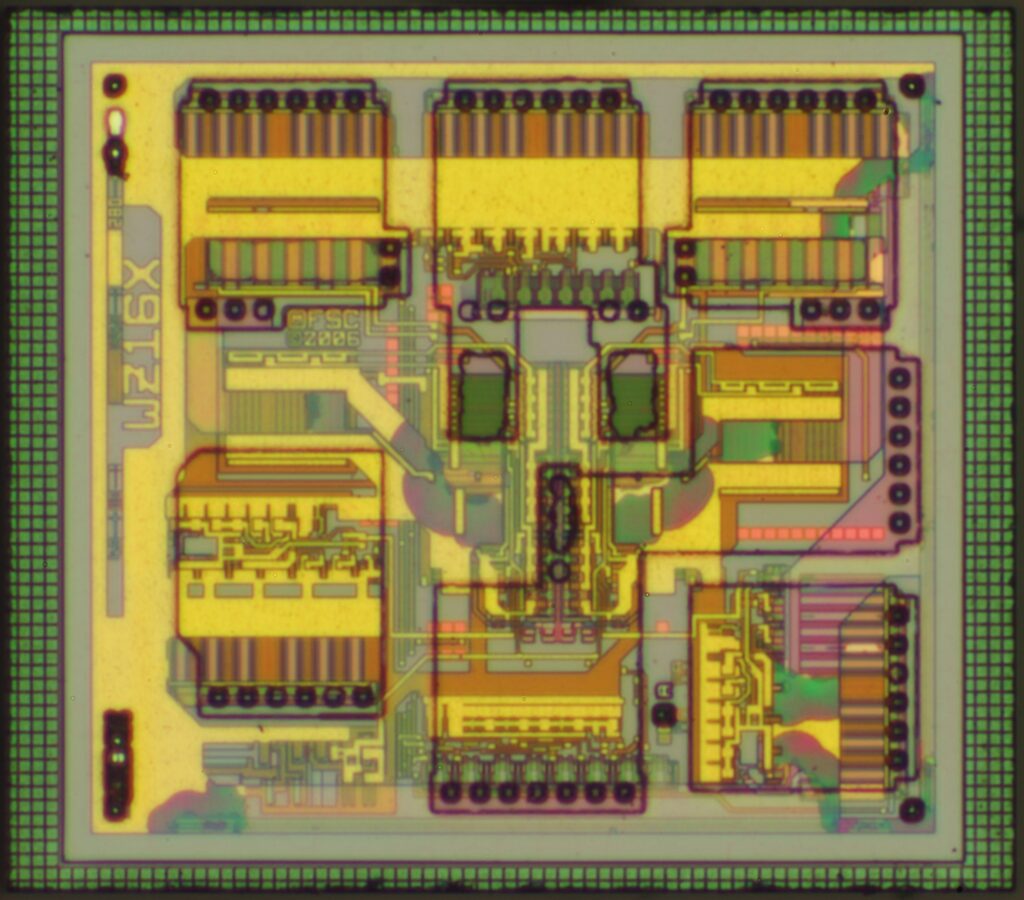

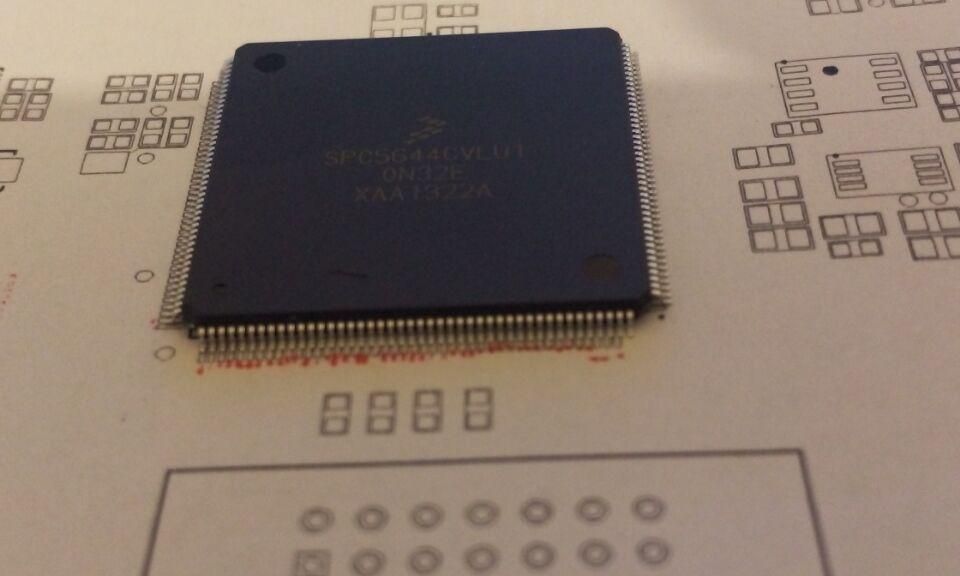

Clone NXP Automobile Microcontroller SPC5606BK0VLL4 Flash Data

Clone NXP Automobile Microcontroller SPC5606BK0VLL4 Flash Data and rewrite the heximal file to a new microprocessor SPC5606BK0V which can provide the same functions as original version, master microcontroller SPC5606BK will be broken in order to release the memory program from flash unit;

The ECSM on this device manages the ECC configuration and reporting for the platform memories (flash memory and SRAM). It does not implement the actual ECC calculation. A detected error (double error for flash memory or SRAM) is also reported to the FCCU. The following errors and indications are reported into the ECSM dedicated registers:

- ECC error status and configuration for flash memory and SRAM

- ECC error reporting for flash memory

- ECC error reporting for SRAM

ECC error injection for SRAM

The PBRIDGE implements the following features:

Duplicated periphery

Master access right per peripheral (per master: read access enable; write access enable)

Checker applied on PBRIDGE output toward periphery

Byte endianess swap capability

The INTC provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high-priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized.

The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed in the process of unlock freescale spc5604pgf1v microcontroller flash memory data. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs.

To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource can not preempt each other when cracking freescale spc5604eef2 microprocessor flash memory.