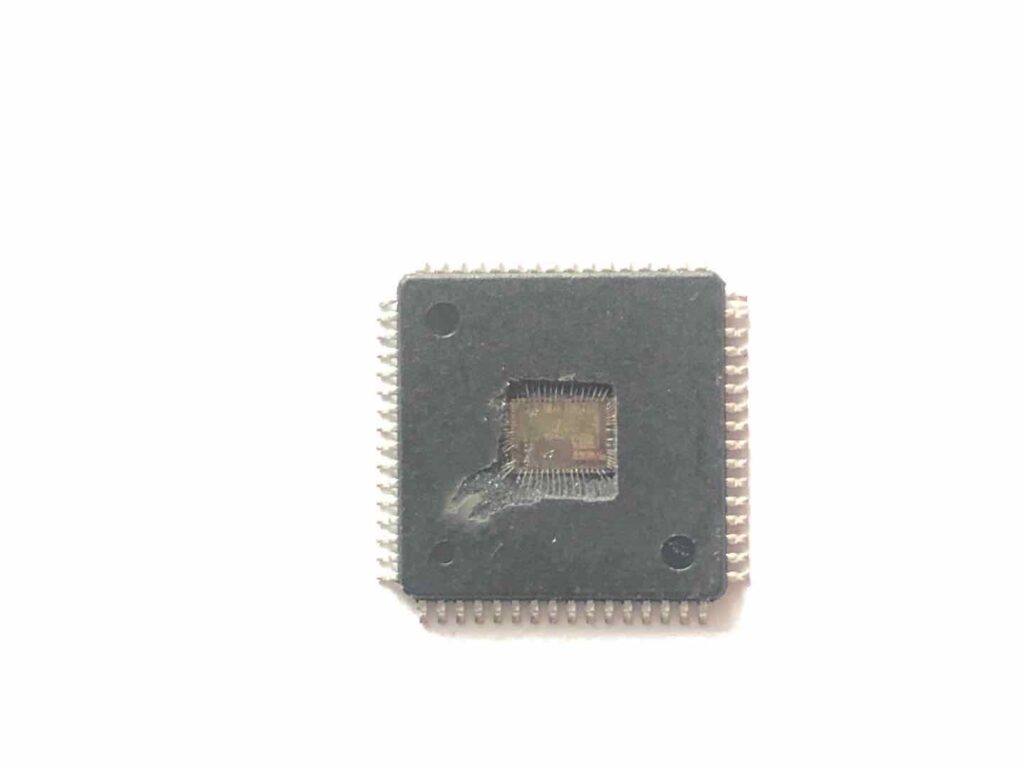

Breaking SPC560P54L5 Locked MCU Flash Memory

Breaking SPC560P54L5 Locked MCU Flash Memory is a process to disable the security added by locked fuse bit, embedded program heximal will be restored from microcontroller spc560p54l5, and copy flash code content to new fresh microprocessor;

The SPC560P34/SPC560P40 SRAM module provides up to 20 KB of general-purpose memory.

The SRAM module provides the following features:

Supports read/write accesses mapped to the SRAM from any master

Up to 20 KB general purpose SRAM

Supports byte (8-bit), half word (16-bit), and word (32-bit) writes for optimal use of memory

Typical SRAM access time: no wait-state for reads and 32-bit writes; 1 wait-state for 8- and 16-bit writes if back-to-back with a read to same memory block

The interrupt controller (INTC) provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems. The INTC handles 128 selectable-priority interrupt sources when unlock automotive microcontroller spc560p34l3 flash memory.

For high-priority interrupt requests, the time from the assertion of the interrupt request by the peripheral to the execution of the interrupt service routine (ISR) by the processor has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR has to be executed.

It also provides a wide number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable as a result of microcomputer spc560p44l3 flash memory content decryption.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol (PCP) for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the same resource can not preempt each other.

The INTC provides the following features:

Unique 9-bit vector for each separate interrupt source

8 software triggerable interrupt sources

16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

Ability to modify the ISR or task priority: modifying the priority can be used to implement the priority ceiling protocol for accessing shared resources.

1 external high priority interrupt (NMI) directly accessing the main core and I/O processor (IOP) critical interrupt mechanism