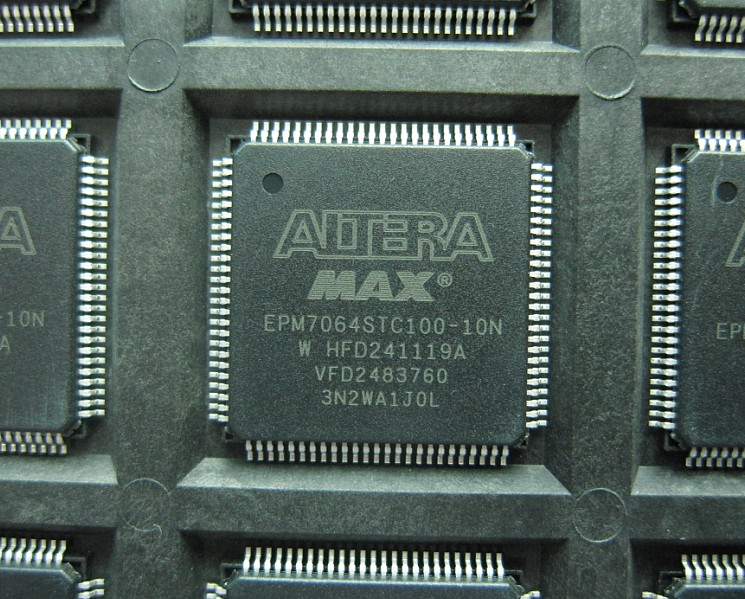

Unlock Altera CPLD EPM7064STC100 Flash Code

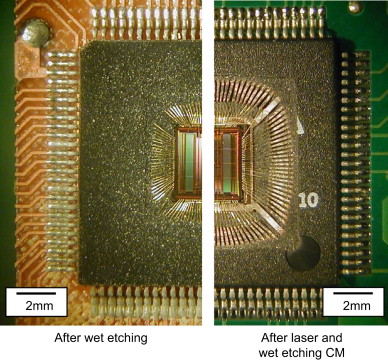

Unlock Altera CPLD EPM7064STC100 Flash Code have to break altera cpld epm7064stc100 flash memory and readout the embedded firmware from chip memory;

MAX 7000A (including MAX 7000AE) devices are high-density, high- performance devices based on Altera’s second-generation MAX architecture. Fabricated with advanced CMOS technology, the EEPROM- based MAX 7000A devices operate with a 3.3-V supply voltage and provide 600 to 10,000 usable gates, ISP, pin-to-pin delays as fast as 4.5 ns, and counter speeds of up to 227.3 MHz. MAX 7000A devices in the -4, -5, -6, -7, and some -10 speed grades are compatible with the timing requirements for 33 MHz operation of the PCI Special Interest Group (PCI SIG) PCI Local Bus Specification.

The MAX 7000A architecture supports 100% transistor-to-transistor logic (TTL) emulation and high-density integration of SSI, MSI, and LSI logic functions. It easily integrates multiple devices including PALs, GALs, and 22V10s devices when unlock cpld epm7032aetc44 eeprom memory code. MAX 7000A devices are available in a wide range of packages, including PLCC, BGA, FineLine BGA, Ultra FineLine BGA, PQFP, and TQFP packages.

When the IEEE Std. 1149.1 (JTAG) interface is used for in-system programming or boundary-scan testing, four I/O pins become JTAG pins.

All Ultra FineLine BGA packages are footprint-compatible via the SameFrameTM feature. Therefore, designers can design a board to support a variety of devices, providing a flexible migration path across densities and pin counts. Device migration is fully supported by Altera development tools. See “SameFrame Pin-Outs” on page 15 for more details.

All FineLine BGA packages are footprint-compatible via the SameFrame feature. Therefore, designers can design a board to support a variety of devices, providing a flexible migration path across densities and pin counts. Device migration is fully supported by Altera development tools. See “SameFrame Pin-Outs” on page 15 for more details