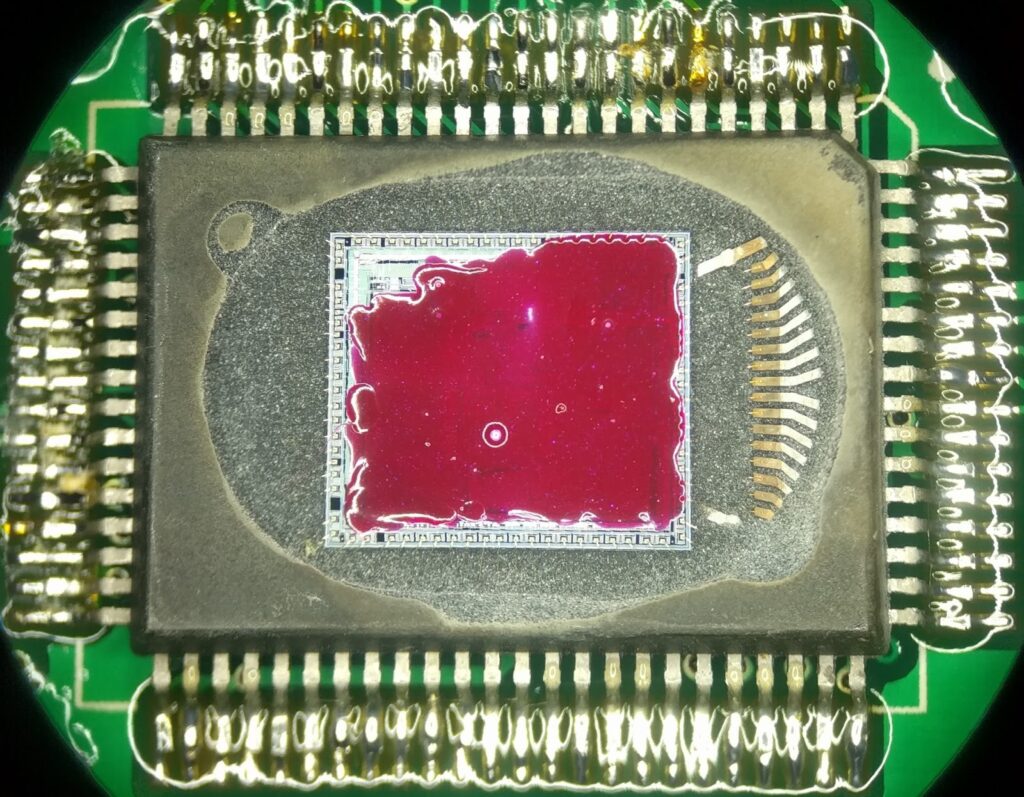

NXP 32Bit Secured MCU SPC5606SF2VLU6R Flash Cracking

NXP 32Bit Secured MCU SPC5606SF2VLU6R Flash Cracking will be able to disable the protection over microprocessor SPC5606SF2VLU6R and turns its status from locked to unlocked one, then readout embedded program from microcontroller SPC5606SF2VLU6R flash memory;

The SRAMC module is the platform SRAM array controller, with integrated error detection and correction.

The main features of the SRAMC provide connectivity for the following interfaces:

- XBAR Slave Port (64-bit data path)

- ECSM (ECC Error Reporting, error injection and configuration)

- SRAM array

The following functions are implemented:

- ECC encoding (32-bit boundary for data and complete address bus)

- ECC decoding (32-bit boundary and entire address)

- Address translation from the AHB protocol on the XBAR to the SRAM array The platform SRAM controller is replicated for each processor.

Every memory access the CPU performs requires at least one system clock cycle for the data phase of the access. Slower memories or peripherals may require additional data phase wait states. Additional data phase wait states may also occur in the process of cracking nxp spc5605bk01m microcontroller flash memory, if the slave being accessed is not parked on the requesting master in the crossbar.

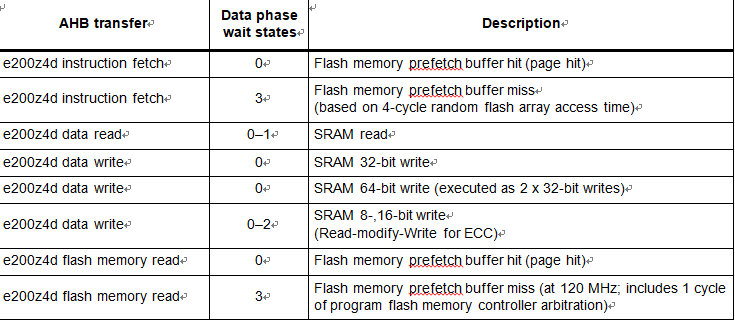

Below table shows the number of additional data phase wait states required for a range of memory accesses.