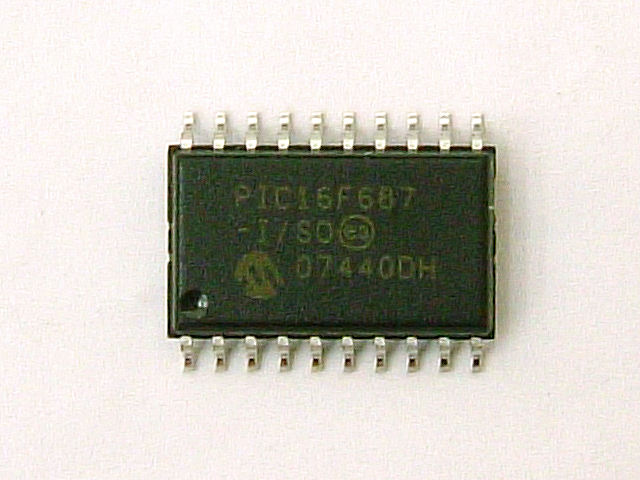

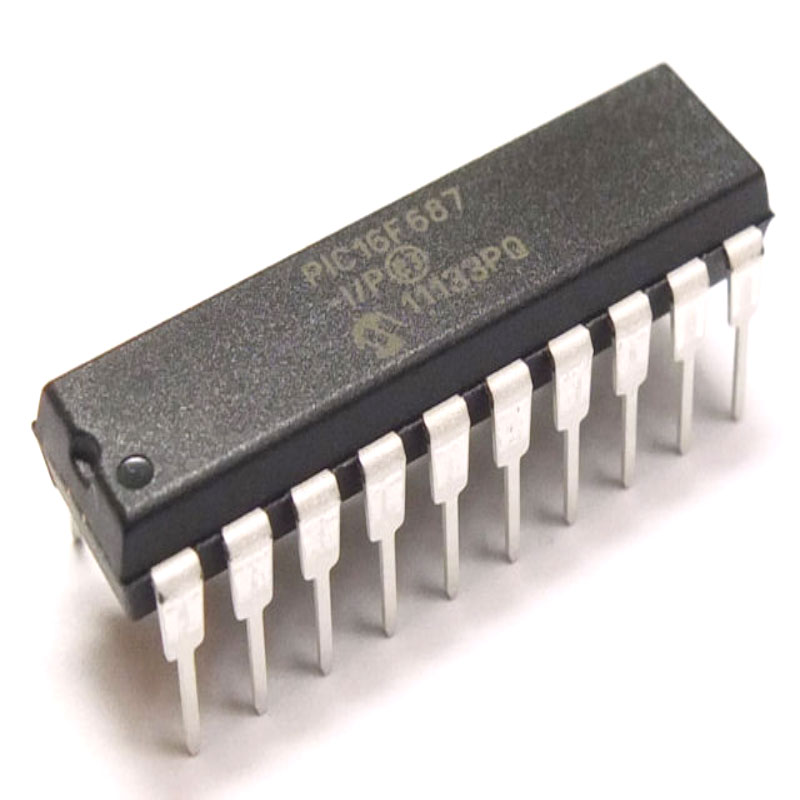

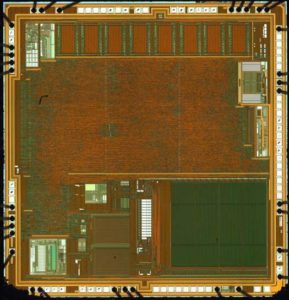

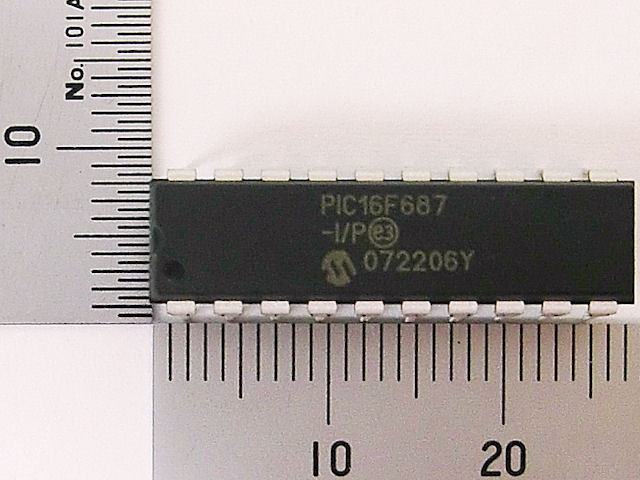

Decapsulate Microprocessor PIC16LF687 Data Eeprom

Decapsulate microprocessor PIC16LF687 data eeprom and restore embedded firmware from secured MCU PIC16LF687 flash program memory and eeprom memory, fuse bit of encrypted microcontroller PIC16LF687 can be attacked or cracked;

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register which can be found directly by Decapsulate Microprocessor PIC16LF687 Data Eeprom. Then, the user must follow a specific write sequence to initiate the write for each byte.

The write will not initiate if the write sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte to Decrypt Microcomputer IC Microchip PIC12C508A. We strongly recommend that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times except when updating EEPROM that is one of the reason for Unlock PIC16F819 Processor Data Memory.

The WREN bit is not cleared by hardware, after a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set to Unlock Microcontroller.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software when Decapsulate Microprocessor PIC16LF687 Data Eeprom.

The steps to write to EEPROM data memory are:

If step 10 is not implemented, check the WR bit to see if a write is in

Write the address to Make sure that the address is not larger than the memory size of the device.

Write the 8-bit data value to be programmed in the EEDATA

Clear the EEPGD bit to point to EEPROM data which Copy AVR Chip ATMEL ATtiny12

Set the WREN bit to enable program

Disable interrupts (if enabled).

Execute the special five instruction sequence:

Write 55h to EECON2 in two steps (first to W, then to EECON2)

Write AAh to EECON2 in two steps (first to W, then to EECON2)

Set the WR bit

Enable interrupts (if using interrupts).

Clear the WREN bit to disable program operations.

At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set (EEIF must be cleared by firmware). If step 1 is not implemented, then firmware should check for EEIF to be set by crack encrypted microprocessor PIC12F752 heximal, or WR to be clear, to indicate the end of the program