Crack MCU ATmega1280V Heximal

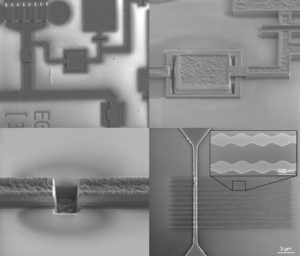

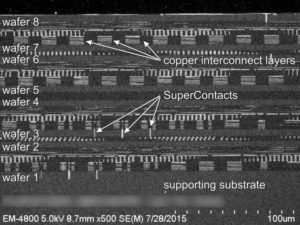

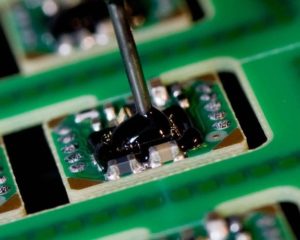

Crack MCU ATmega1280V starts from disable the tamper resistance system of Microcontroller, decapsulate the silicon package of ATmega1280V and extract the Heximal out from the memory;

Crack MCU ATmega1280V starts from disable the tamper resistance system of Microcontroller, decapsulate the silicon package of ATmega1280V and extract the Heximal out from the memory

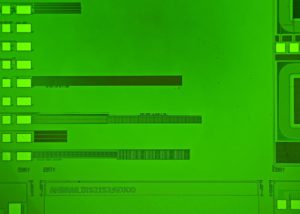

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

AVCC is the supply voltage pin for the A/D Converter, PC3:0, and ADC7:6. It should be externally connected to VCC, even if the ADC is not used. If the ADC is used, it should be connected to VCC through a low-pass filter. Note that PC6…4 use digital supply voltage, VCC.

In the TQFP and QFN/MLF package, ADC7:6 serve as analog inputs to the A/D converter. These pins are powered from the analog supply and serve as 10-bit ADC channels.

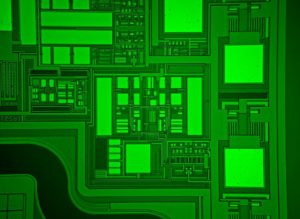

The ATMEGA1280V is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega1280V achieves through puts approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed to facilitate the Microcontroller copying.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle.

The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

Tags: crack mcu encrypted archive,crack mcu encrypted code,crack mcu encrypted content,crack mcu encrypted data,crack mcu encrypted eeprom,crack mcu encrypted file,crack mcu encrypted firmware,crack mcu encrypted information,crack mcu encrypted memory,crack mcu encrypted program