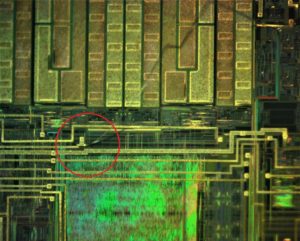

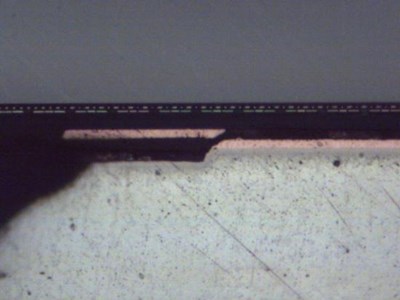

Crack Chip ATmega2561V Heximal

Crack Chip ATmega2561V and readout Heximal from its flash and eeprom memory, the process will normally takes no longer than 3 days and success rate is 100% guarantee due to the solution of ATmega2561V IC breaking has been developed for years and it is mature and stable;

Crack Chip ATmega2561V and readout Heximal from its flash and eeprom memory, the process will normally takes no longer than 3 days and success rate is 100% guarantee due to the solution of ATmega2561V IC breaking has been developed for years and it is mature and stable

Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated when IC PIC16F884 code extraction.

The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running. Port F serves as analog inputs to the A/D Converter. Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used if MCU PIC16F886 Software extraction.

Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated.

The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS), and PF4(TCK) will be activated even if a reset occurs after Chip PIC16F87 hexima extraction .

Port F also serves the functions of the JTAG interface. Port G is a 6-bit I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability.

As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running if MCU PIC16C710 program reading.

Port G also serves the functions of various special features of the ATmega2561 as listed on page 102.

Port H is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port H output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port H pins that are externally pulled low will source current if the pull-up resistors are activated. The Port H pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port J is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port J output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port J pins that are externally pulled low will source current if the pull-up resistors are activated. The Port J pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Tags: crack chip archive,crack chip bin,crack chip code,crack chip content,crack chip data,crack chip eeprom,crack chip file,crack chip firmware,crack chip hexi,crack chip information,crack chip memory,crack chip program