Clone TMS320F28026 Microprocessor Software Data

Two capture inputs (CAP1 and CAP2) can be used to interface the on-chip QEP circuit with a quadrature encoder pulse. Full synchronization of these inputs is performed on-chip. Direction or leading-quadrature pulse sequence is detected in the process of Clone TMS320F28026 Microprocessor Software Data, and GP timer 2 or 3 is incremented or decremented by the rising and falling edges of the two input signals (four times the frequency of either input pulse).

A simplified functional block diagram of the ADC module is shown in Figure 12. The ADC module consists of two 10-bit ADCs with two built-in sample-and-hold (S/ H) circuits. A total of 16 analog input channels is available on the TMS320x240.

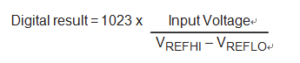

Eight analog inputs are provided for each ADC unit by way of an 8-to-1 analog multiplexer to execute Locked ST62T09 Heximal Cloning. Minimum total conversion time for each ADC unit is 6.1 s. Total accuracy for each converter is ±1.5 LSB. Reference voltage for the ADC module needs to be supplied externally through the two reference pins, VREFHI and VREFLO. The digital result is expressed as:

Functions of the ADC module include:

Two input channels (one for each ADC unit) that can be sampled and converted simultaneously only after Unlock MCU ATMEGA164V Program

Each ADC unit can perform single or continuous S/H and conversion operations.

Two 2-level-deep FIFO result registers for ADC units 1 and 2

ADC module (both A/D converters) can start operation by software instruction, external signal transition on a device pin, or by event-manager events on each of the GP timer/compare output and the capture 4 pins. The ADC control register is double-buffered (with shadow register) and can be written to at any time to facilitate the process of Crack MCU ATMEGA1284PV Heximal. A new conversion of ADC can start immediately or when the previous conversion process is completed according to the control register bits. At the end of each conversion, an interrupt flag is set and an interrupt is generated if it is unmasked/enabled the IC Breaking.