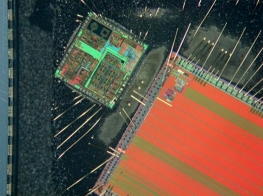

Attack ARM MCU STMicroelectronics STM32F105RCT6TR

Attack ARM MCU STMicroelectronics STM32F105RCT6TR

Hereby we would like to introduce the features of ARM STM32F105RCT6TR which will help to Attack ARM MCU STMicroelectronics STM32F105RCT6TR:

Features

– 72 MHz maximum frequency, 1.25 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state memory

LQFP100 14 × 14 mm

LQFP64 10 × 10 mm access

– Single-cycle multiplication and hardwaredivision

Memories

– 64 to 256 Kbytes of Flash memory

– up to 64 Kbytes of general-purpose SRAM Clock, reset and supply management

– 2.0 to 3.6 V application supply and I/Os

– POR, PDR, and programmable voltage detector (PVD)

– 3-to-25 MHz crystal oscillator

– Internal 8 MHz factory-trimmed RC

– Internal 40 kHz RC with calibration

– 32 kHz oscillator for RTC with calibration Low power

– Sleep, Stop and Standby modes

– VBAT supply for RTC and backup registers

2 × 12-bit, 1 µs A/D converters (16 channels)

– Conversion range: 0 to 3.6 V

– Sample and hold capability

– up to 2 MSPS in interleaved mode 2 × 12-bit D/A converters DMA: 12-channel DMA controller

– Supported peripherals: timers, ADCs, DAC, I2Ss, SPIs, I2Cs and USARTs

Up to 10 timers with pinout remap capability

– Up to four 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

– 1 × 16-bit motor control PWM timer with dead-time generation and emergency stop

– 2 × watchdog timers (Independent and Window)

– SysTick timer: a 24-bit downcounter

– 2 × 16-bit basic timers to drive the DAC Up to 14 communication interfaces with pinout remap capability

– Up to 2 × I2C interfaces (SMBus/PMBus)

– Up to 5 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)

– Up to 3 SPIs (18 Mbit/s), 2 with a multiplexed I2S interface that offers audio class accuracy via advanced PLL schemes

– 2 × CAN interfaces (2.0B Active) with 512 bytes of dedicated SRAM

– USB 2.0 full-speed device/host/OTG controller with on-chip PHY that supports HNP/SRP/ID with 1.25 Kbytes of dedicated SRAM

– 10/100 Ethernet MAC with dedicated DMA and SRAM (4 Kbytes): IEEE1588 hardware support, MII/RMII available on all packages

Device summary

– Cortex-M3 Embedded Trace Macrocell™

Up to 80 fast I/O ports

– 51/80 I/Os, all mappable on 16 external

interrupt vectors and almost all 5 V-tolerant

CRC calculation unit, 96-bit unique ID